SI-01-PCB特性阻抗

本博客记录PCB阻抗与叠层设计的参考思路。

特性阻抗

特性阻抗为高频信号在均匀传输线上的等效阻抗。信号线在传输信号时会与参考平面(地平面、电源平面)建立电场产生瞬间电流,由电压电流V/I得等效阻值Z0,具体取决于介电常数ε0与每单位长度的电容CL。

而根据产生电场的条件,传输介质介电常数ε0不变的情况下,信号传输线与参考平面的距离d越近/面积(线宽)S越大,等效电容(寄生电容)C越大,进而等效阻抗Z0越小。 C = ε0 * S/d

根据上式也能得出结论,对于电源/地两个参考平面,其截面大阻抗低(约1Ω),对于带状线与微带线线宽窄阻抗高(约60-90Ω)。

特征阻抗的影响因素包括线宽、铜厚、板厚、层数、基板材料、表面工艺,可根据实际的阻抗设计值、阻抗公差计算线宽线距。介质越厚、线距越大阻抗越大;介电常数、铜厚、线宽、阻焊厚度越大阻抗越小。

介电常数

对FR-4,介电常数为3.9-4.5;

对聚四氟乙烯,介电常数为2.2-3.9;

阻焊厚度

刷绿油/黑油(阻焊)一次使单端阻抗降低2Ω,差分阻抗降低8Ω。两次时翻倍,三次时不再变化。

阻抗计算

传输线就像水管,水管粗细突变时水流会被阻拦。同样,一根传输线上阻抗突变意味着信号会发生反射,进而产生噪声干扰正常信号。

做阻抗的目的就是减少信号反射点,降低传输损耗。一般在设计fclock>100MHz的高速电路时就需要做阻抗。

可使用嘉立创阻抗计算或者SI9000输入参数进行线宽线距计算。以嘉立创为例,计算时需要区分单端/差分阻抗与共面单端/共面差分阻抗。

单端阻抗:单根信号线与参考平面之间的阻抗

差分阻抗:差分线对间、与相邻参考层间的耦合阻抗。

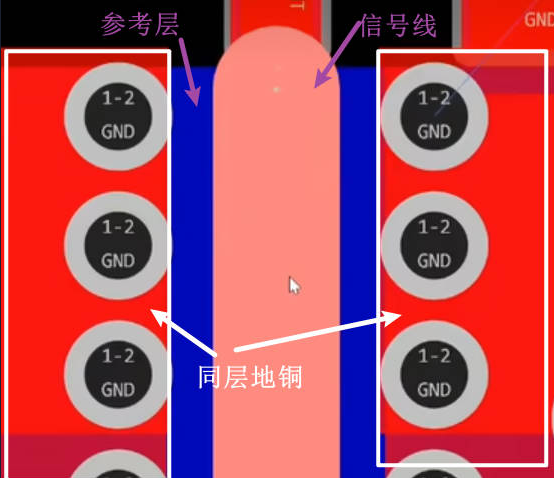

共面单端阻抗:单根信号线与参考平面间(尽量完整参考地)、以及与同层两侧地铜皮的耦合阻抗。

共面单端阻抗

共面单端阻抗

共面差分阻抗:差分信号线现对间、与参考平面间(尽量完整参考地)、与同层两侧地铜皮的的耦合阻抗。共面差分则与之类似。

共面地是为了抑制串扰、增加回流路径。对于多层板,可利用单端阻抗和差分阻抗计算设计,但是对于以下情况,通常需要使用共面单端与共面差分:

- 两层板。板厚过大,根据公式限制较小阻抗时线宽较大(可能达到100mil),而且两层板通常没有完整的参考地。

- 射频天线

- 高速信号

常用接口

- RS232:可不做(低频高压摆特性)

- LVDS:100Ω差分

- CAN:100Ω差分

- USB:90Ω差分

- SATA:90Ω差分

- Ethernet:CAN:100Ω差分

参考资料

- 传输线的物理基础(四):传输线的特征阻抗-CSDN博客

- 嘉立创阻抗计算

- 如何理解共面差分阻抗,共面单端阻抗?有哪些影响因素?如何用嘉立创阻抗计算神器计算阻抗值?哔哩哔哩

- 差分走线有5个常见误区,你是否出现? - 知乎

- 常用通信阻抗要求 | WwWangGuan

————————— End —————————

“没有调查,没有发言权。”–毛泽东《反对本本主义》