FPGA-01-关于ZYNQ

该博文记录学习FPGA的演变过程、主要功能、性能差异等基础知识(感觉并没有什么参考意义….

PLD器件

FPGA: Field Programmable Gate Array,即现场可编程门阵列,属于可编程器件PLD(Programmable Logic Device),类似的有PLA、PAL、CPLD等器件。

PLA与PROM

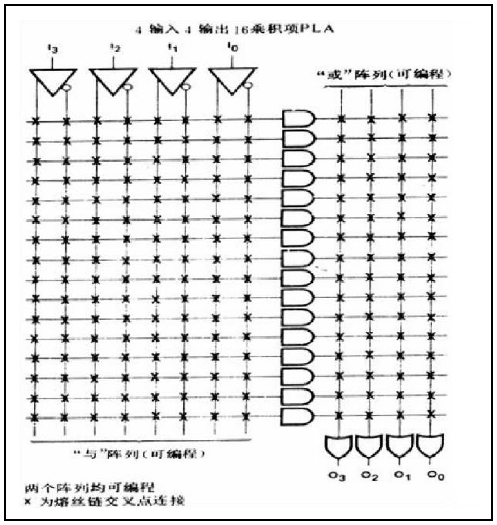

PLA与PROM为早期反熔丝型PLD电路。PLA(Programmable Logic array)中通过与门、非门构成“与平面”,“或平面”,以及一次性的编程矩阵。

PLA内部结构

PLA内部结构

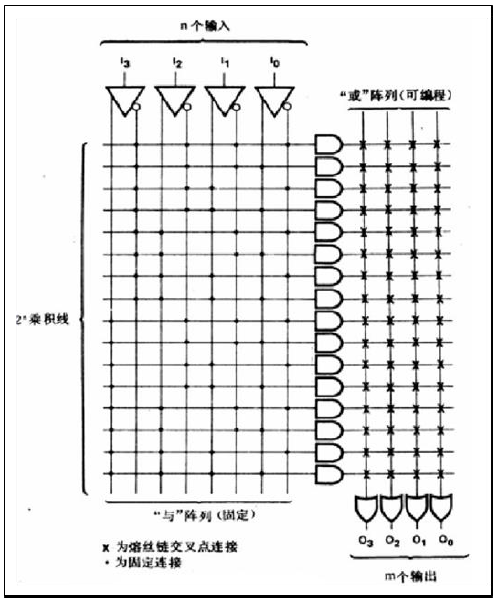

可编程只读存储器PROM(Programmable Read-Only Memory)与PLA类似,均是通过“与连接矩阵与“或连接矩阵”组成,但是PROM的结构上与连接矩阵固定,仅”或矩阵”可进行一次编程,如下图。

PROM内部结构

PROM内部结构

PAL与GAL

在PLA与PROM的基础上又延伸出其他两种类型,即PAL(Programmable Array Logic)和GAL(Generic Array Logic)。

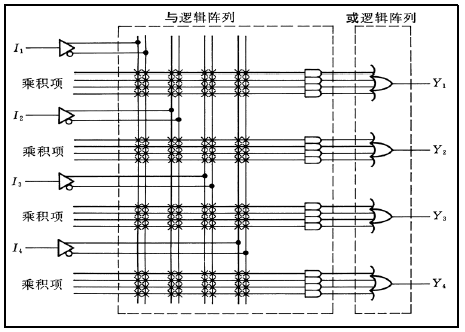

其中PAL相对于PROM结构类似,只是PAL是仅”与连接矩阵”可编程,仍然为反熔丝工艺,仅可编程1次。

PAL根据输出电路工作模式可分为三类:

- 三态输出

- 寄存器输出

- 互补输出

PAL内部结构

PAL内部结构

GAL相对于PAL改进:

- CMOS工艺,电可擦除,可多次编程

- 可编程的输出逻辑宏单元OLMC(Output Logic Macro Cell)

其中OLMC可通过编程控制GAL输出,覆盖PAL的三种模式。

CPLD与FPGA

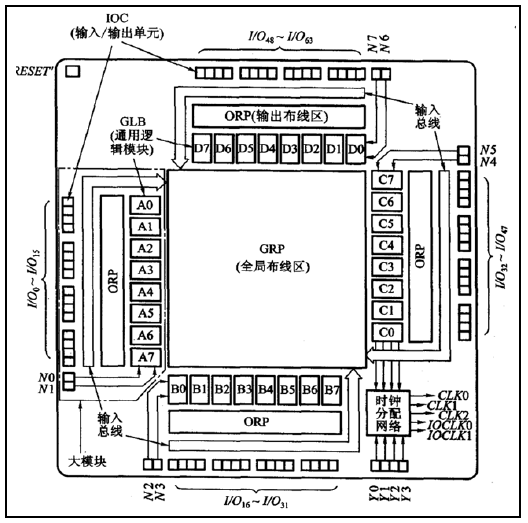

复杂可编程逻辑器件CPLD(Complex Programmable Logic Device)可以看作若干PLA与可编程连接矩阵的集合。内部结构如图。

CPLD内部结构

CPLD内部结构

FPGA内大量使用LUT查找表和寄存器,可分为SRAM、反熔丝、Flash三种类型,包括可编程的:

- 逻辑块

- 布线资源

- IO口

FPGA与CPLD对比

FPGA与CPLD对比

FPGA的应用场景对比单片机和ARM,主要优势9是灵活高效、高吞吐量、低批量延时、快速并行运算、可重构、可重复编程、可实现定制性能和定制功耗。

ZYNQ

Xilinx内的ZYNQ系列芯片内包括一块Cortex-A9的硬件ARM处理器,称为为PS。其余的逻辑部分,称为PL,PL上可以使用逻辑块搭载MicroBlaze软核处理器。

PS 端

ZYNQ内除去ARM外,还包括应用处理单元APU(Application Processing Unit)、扩展外设、cache存储器、存储器接口、互联接口、时钟发生电路。

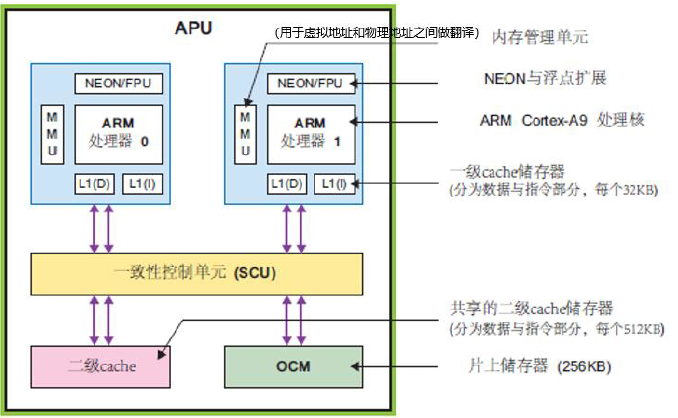

APU

- 双ARM核、NEONTM媒体处理引擎MPE(Media Processing Engine)、浮点计算单元FPU(Floating Point Unit)、内存管理单元MMU(Memory Management Unit)、一级cache存储器(指令+数据)

- 一致性控制单元SCU(Snoop Control Unit):ARM与OCM和二级cache之间的连接桥。可用加速一致端口ACP(Accelerator Coherency Port)管理PS与PL的访问

- 二级cache、片上存储器OCM(On Chip Memory),包括256kB的RAM和128kB的BootRAM。

存储器接口

ZYNQ-7000系列存储器接口包括动态+静态口。

动态存储器控制器

- 核心存储控制器和调度器DDRC

- AXI存储器端口接口DDRI

- 数字PHY及控制器DDBP,可用于DDR2/3、DDR3L、LPDDR2

静态存储控制器

SMC(Static Memory Controller),可用作NAND闪存控制器、或并口存储器控制器,支持NAND闪存、NOR闪存、异步SRAM。

QSPI

程序烧录,程序固化。

外部接口

PS和外部通信主要通过复用的输入/输出MIO(Multiplexed Input/Output,MIO)实现,直接连接在PS端。但扩展的MIO即EMIO需要通过PL端转接,QSPI、USB、SMC不适用于PL的EMIO接口。

出去4组32位的GPIO外,对外接口还包括各2组:SPI、I2C、CAN、UART、SD、USB、GigE(Ethernet)。

PL端

Xilinx FPGA芯片的组成部分:可编程输入输出单元IOB、可配置逻辑块CLB、嵌入式块RAM、布线资源、底层内嵌功能单元、底层内嵌专用硬核等。

IOB

需要注意,FPGA每个Bank的VCC电压不同,一个Bank仅有一个电压。

I/O组被分类为高性能HP(High Performance)和高范围HR(High Range)。

- HP:VCC为1.8V,常作连接存储器和其他芯片的高速接口

- HR:VCC为3.3V,适合各种IO标准

HP与HR均支持单端、差分输入,具体可以查阅引脚说明。

每个IOB包括IOSERDER,可作串转并或并转串。

CLB

CLB指可编程逻辑块,逻辑单元最小规模。Slice片是CLB的子单元。

ZYNQ的片是由4个查找表(LUT)+8触发前+其他逻辑组成的。

BRAM

嵌入式块RAM,用于生成RAM、ROM、FIFO及移位寄存器等常用的存储模块。

ZYNQ的BRAM由60个存储块组成:

- 每个块RAM由2个18kB的BRAM组成;

- 以块为单位使用;

- 3类分组,即BRAM(36kB);BRAM(18kB)+BRAM(18kB),BRAM+FIFO。由于仅包括1个FIFO Logic,只能生成一组FIFO控制信号。

使用块RAM即在片内用小物理空间存储大量数据。

硬核

ZYNQPL端内嵌XADC,即两个模数转换器。且有接口可以连接至PS端。

————————— End —————————

大梦谁先觉,平生我自知。–《三国演义》